Write Verilog Code for 4:1 MUX using Gate Level Modelling TMSY. The above waveform displays the VHDL Code for 2 to 4 decoder implementation result. IMPLEMENTATION OF 416 DECODER USING 24 DECODER 416 DECODER USING 24 DECODER. VHDL Code for 2 to 4 decoder using case statement

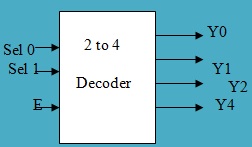

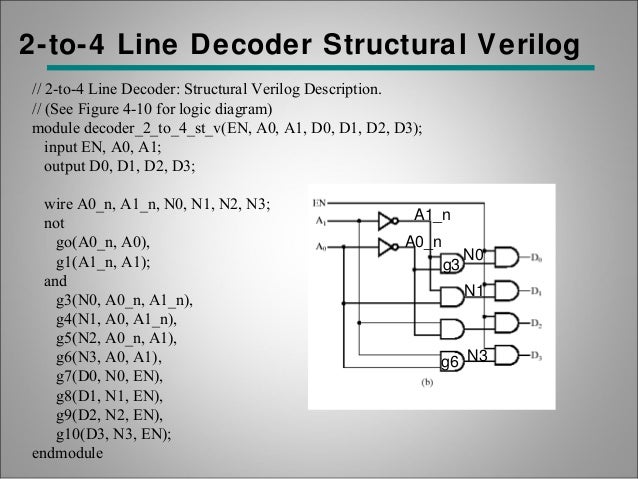

Here we provide example code for all 3 method for better understanding of the language. Similar to Encoder Design, VHDL Code for 2 to 4 decoder can be done in different methods like using case statement, using if else statement, using logic gates etc. VHDL Code of 2 to 4 decoder can be easily implemented with structural and behavioral modelling. Decoders are used to decode data that has been previously encoded using a binary, or possibly other, type of coded format. Binary decoder can be easily constructed using basic logic gates. It can be 2-to-4, 3-to-8 and 4-to-16 line configurations. VHDL Code for 2 to 4 decoder using logic gatesīinary decoder has n-bit input lines and 2 power n output lines.VHDL Code for 2 to 4 decoder using if else statement.VHDL Code for 2 to 4 decoder using case statement.The enable inputs must be ON for the decoder to function, otherwise its outputs assumes a ‘disabled’ output code word. 2 to 4 Decoder design using logic gates Objective: After designing two verilog decoders from 2 data input to 4 data output, connect these in order to create a 3-8 model and test for value. Write a verilog program for 2 to 4 decoder A decoder is a multiple input, multiple output logic circuit that converts coded inputs into coded outputs where the input and output codes are different.

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. Archives

May 2023

Categories |

RSS Feed

RSS Feed